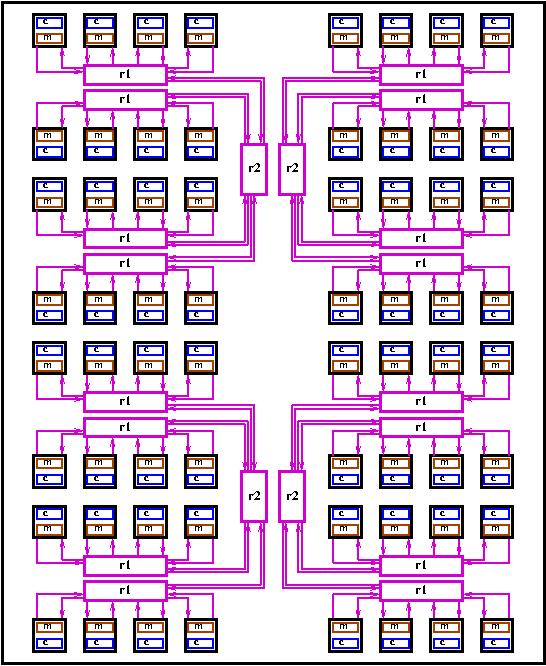

The interconnection of the cores

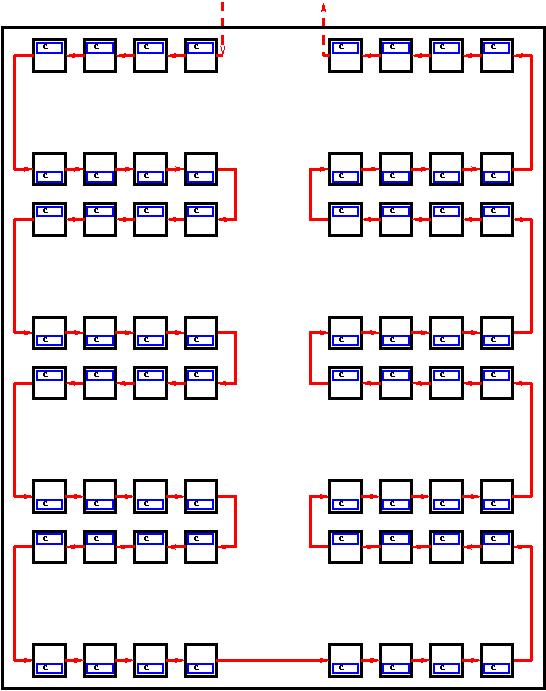

Each core (a blue rectangle inside a black square, labeled c) is directly connected to its next neighbor (i.e. core i is connected to core i+1) (red arrows).

The next core connections are used to allocate harts (fork), send/receive continuation values (p_swcv/p_lwcv ; e.g. iterator) and send join signals.

An LBP processor can be self-contained (there is a first core with no predecessor and a last core with no successor) or it can be linked to other identical chips to extend the line of cores.

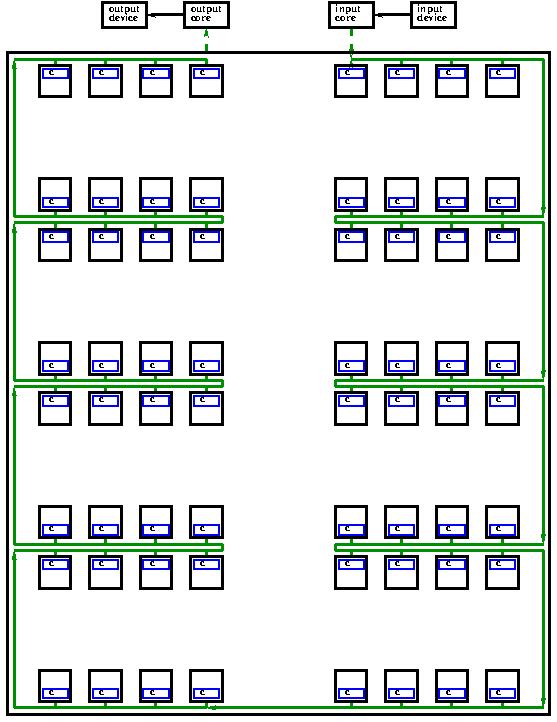

Each core is indirectly connected to any predecessor through a uni-directional line (i.e. core i (i>0) is connected to core i-k (0<k<=i)) (green arrows).

The uni-directional line is used to send results (p_swre/p_lwre ; e.g. reduction) and to send join addresses.

The predecessor core connection line can be extended outside the LBP chip.

The set of cores can be extended by an input core (placed after the last core and able to serve an input to any other core) and an output core (placed before the first core and able to receive an output from any other core).

The serial links are not intended for intense data communications, i.e. memory reads and writes.

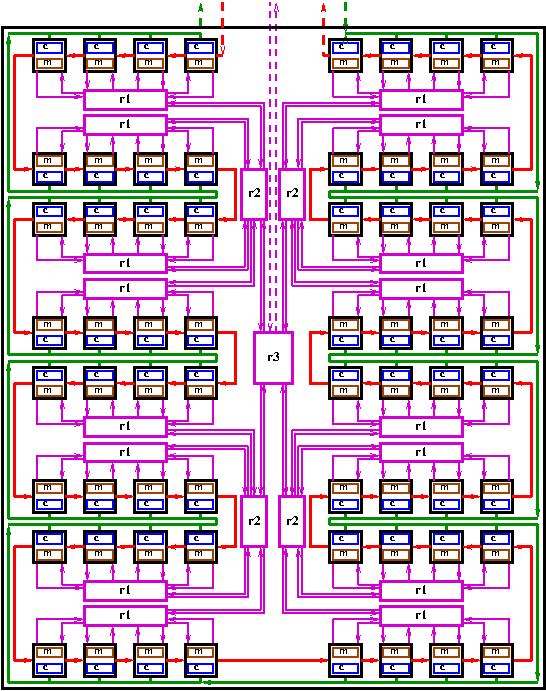

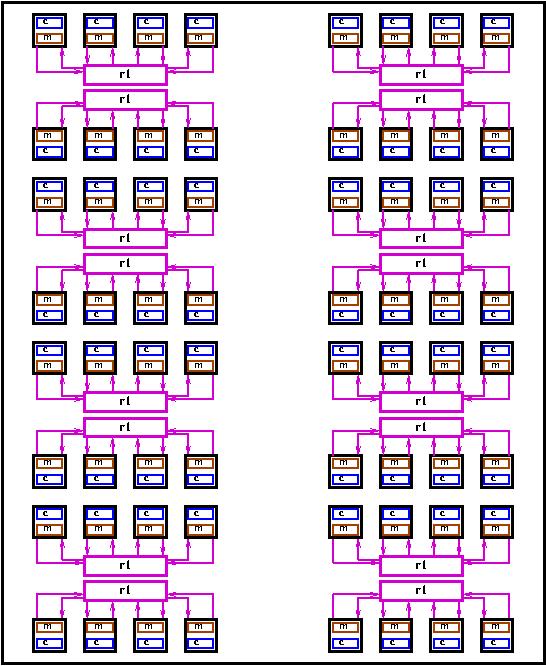

For memory accesses, each core has a private access to its code, local data and global data memory banks (only the global memory banks are represented on the figure, labeled m).

Each core has also a private access to a level one router connected to four global data memory banks.

Each level one router has a private access to each of the four memory banks.

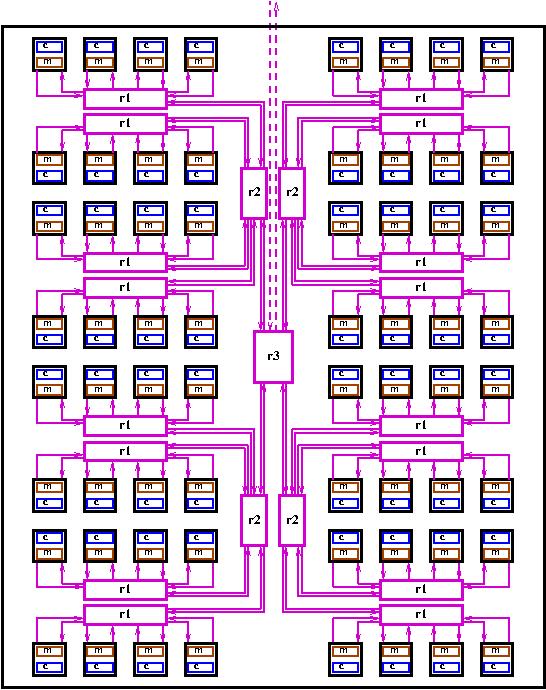

Each level one router has four private accesses (represented as a single line starting from r1 and ending at r2) to a level two router (a single line from r2 to r1 represents four links) indirectly connected to sixteen global data memory banks.

Each level two router has four private accesses (represented as a single line starting from r2 and ending at r3) to a level three router (a single line from r3 to r2 represents four links) indirectly connected to 64 global data memory banks.

The level three router can be linked to an external level four router or DRAM memory controller.

The full view of the LBP processor, including the next core links (red), the predecessor cores link (green arrow), the three level of routers (magenta) and the optional extension (dashed lines).